如果說在過去五年左右的芯片設(shè)計中有一個突出的、全行業(yè)的趨勢��,那無疑就是小芯片(chiplet)的使用越來越多。隨著芯片制造商希望它們能解決從芯片制造成本到設(shè)計的整體可擴展性等方方面面的問題�����,微型裸片已成為越來越普遍的特征。無論是簡單地將以前的單片 CPU 拆分成幾塊���,還是將47 個小芯片放在一個封裝上,小芯片已經(jīng)在今天的芯片設(shè)計中發(fā)揮著重要作用��,芯片制造商已經(jīng)明確表示它只是將來會成長����。

與此同時,經(jīng)過 5 年多的認(rèn)真���、大批量使用��,小芯片和支撐它們的技術(shù)似乎終于在設(shè)計方面達到了一個拐點�。芯片制造商已經(jīng)對小芯片的好處(和壞處)有了更充分的了解����,封裝供應(yīng)商已經(jīng)改進了放置小芯片所需的超精確方法,工程團隊已經(jīng)解決了用于讓小芯片相互通信的通信協(xié)議��。

簡而言之��,小芯片不再是需要驗證的實驗性設(shè)計,而是已成為芯片制造商可以依賴的經(jīng)過驗證的設(shè)計�����。隨著對小芯片技術(shù)的日益依賴�����,對設(shè)計路線圖和穩(wěn)定性的需求也隨之而來——對設(shè)計標(biāo)準(zhǔn)的需求也順勢而至�。

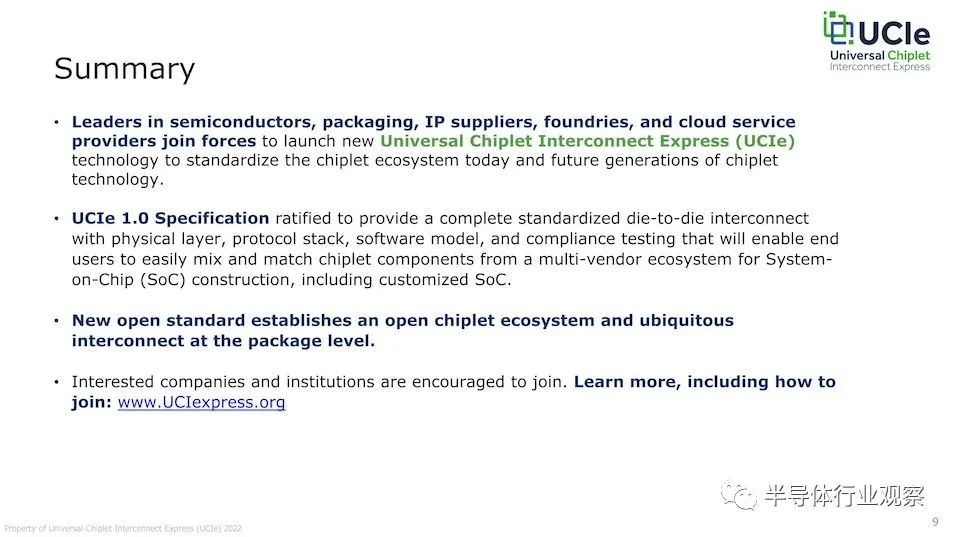

為此,今天英特爾����、AMD、Arm 和所有三個領(lǐng)先的代工廠商齊聚一堂���,宣布他們正在為小芯片互連制定一個新的開放標(biāo)準(zhǔn)����,該標(biāo)準(zhǔn)被恰當(dāng)?shù)孛麨閁CIe(Universal Chiplet Interconnect Express,). 這個名字從非常成功的 PCI-Express 標(biāo)準(zhǔn)中汲取靈感�����,相關(guān)公司正在與 UCIe 一起創(chuàng)建連接小芯片的標(biāo)準(zhǔn)�����,目標(biāo)是制定一套標(biāo)準(zhǔn),不僅簡化所有相關(guān)參與者的流程����,而且引領(lǐng)走向來自不同制造商的小芯片之間的完全互操作性,允許芯片在芯片制造商認(rèn)為合適的情況下混合和匹配小芯片�。

換句話說�����,要從小芯片中構(gòu)建一個完整且兼容的生態(tài)系統(tǒng)����,就像今天的基于 PCIe 的擴展卡的生態(tài)系統(tǒng)一樣。

與 PCIe 的比較適用于多個層面��,這可能是快速了解 UCIe 小組目標(biāo)的最佳方式����。不僅新標(biāo)準(zhǔn)以開放的方式提供,相關(guān)公司還將在今年晚些時候建立一個正式的聯(lián)盟組來管理 UCIe 并進一步開發(fā)它����。同時�,從一般技術(shù)的角度來看��,小芯片的使用是集成電路不斷整合的最新舉措��,因為越來越小的晶體管允許越來越多的功能被集成到芯片上����。從本質(zhì)上講,到目前為止���,一直在擴展卡或單獨芯片上的功能正在開始進入芯片/SoC 本身�����。所以就像 PCIe 調(diào)節(jié)這些部件如何作為擴展卡一起工作一樣�,

最終��,UCIe 背后的團隊的既定目標(biāo)是為小芯片建立一個開放且無處不在的生態(tài)系統(tǒng)���。無論這意味著簡單地將某些物理方面標(biāo)準(zhǔn)化以簡化制造���,還是實現(xiàn)真正的混合匹配設(shè)置,客戶可以從多個芯片(let)制造商處請求使用小芯片構(gòu)建的芯片����,這些都需要一個強大的基礎(chǔ)標(biāo)準(zhǔn)來實現(xiàn)�。芯片制造行業(yè)的主要參與者都在支持 UCIe 以實現(xiàn)這一目標(biāo)����。

為什么是小芯片?

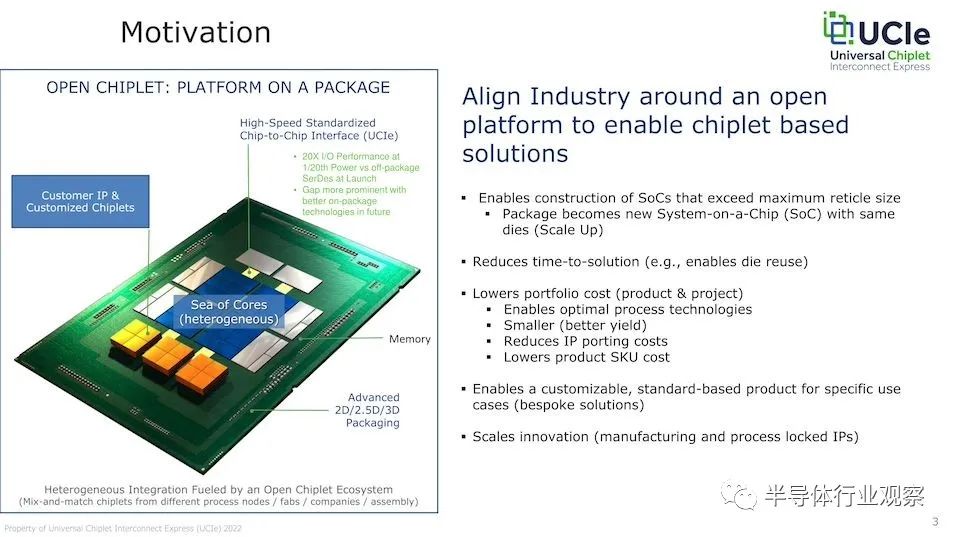

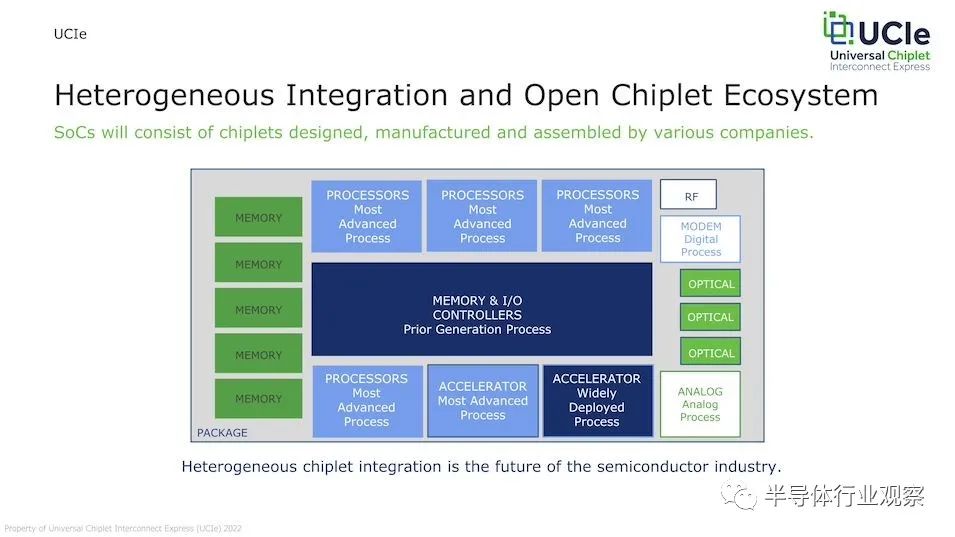

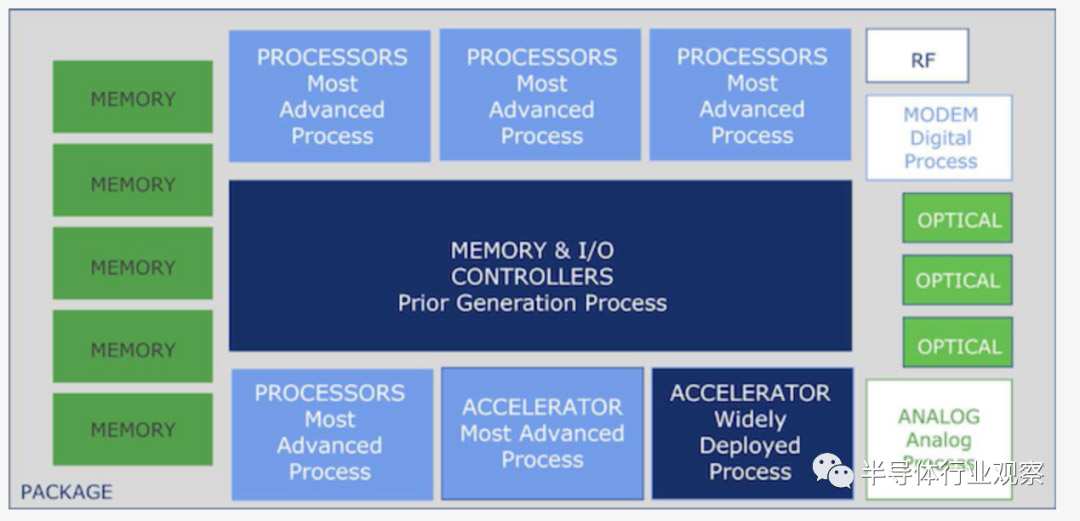

反過來���,發(fā)生所有這一切的原因是Chiplet被越來越多地使用——在某些情況下更是唯一選擇����。小芯片已經(jīng)被用于混合來自多個芯片制造商或來自多個工藝節(jié)點的裸片��,并且它們被用于構(gòu)建由于標(biāo)線限制而無法實現(xiàn)的大型芯片��。所有這些都是由某種方式的經(jīng)濟驅(qū)動(如不是為芯片的每個部分使用昂貴的尖端節(jié)點)����,或者是希望以一種比花費數(shù)年時間流片單片芯片更方便的方式結(jié)合不同制造商的 IP����。可以肯定的是�����,單片芯片作為一個整體并沒有完全消失(移動數(shù)據(jù)仍然很昂貴),但芯片設(shè)計的經(jīng)濟性正在無情地推動芯片在更多情況下的使用�����。

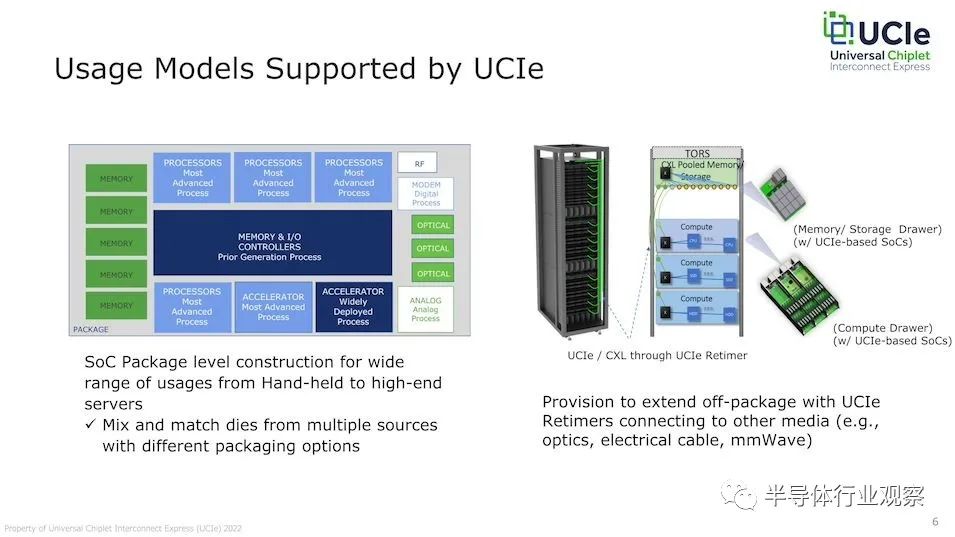

與此同時��,對性能和效率的推動也推動了對小芯片的持續(xù)興趣����。或者更具體地說����,推動了將更多功能集成到單個芯片封裝上的愿望。PCIe 盡管速度很快���,但按照芯片標(biāo)準(zhǔn)來看仍然很慢���;從 CPU 到控制器(然后再返回)的長走線長度會增加很多延遲,并且將數(shù)據(jù)推送到那么遠的地方在功率方面相對昂貴���。因此����,芯片制造商越來越希望將這些功能集成到芯片上,以降低延遲并降低功耗����。對于小芯片(以及 UCIe),這意味著能夠?qū)⑿阅芴岣?20 倍以上�����,并將功耗降低大致相同的數(shù)量�����。

UCIe 1.0:新的 Die-To-Die 規(guī)范��,頂部有 PCIe 和 CXL�,今日上市

深入研究 UCIe 規(guī)范的第一個修訂版�����,我們發(fā)現(xiàn)一些非常簡單的東西��,以及圍繞當(dāng)今封裝技術(shù)的功能非常明確地設(shè)計的東西�����。今天,UCIe 帶來的不是新技術(shù)����,而是當(dāng)前技術(shù)的不同實現(xiàn)之間的標(biāo)準(zhǔn)化,以便每個人都有共同的基礎(chǔ)來工作����。

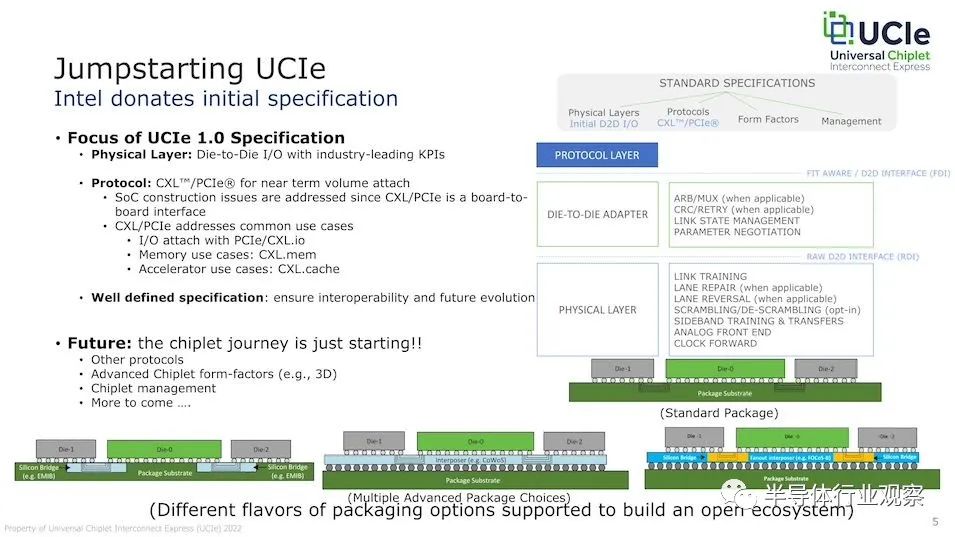

不足為奇的是,這個初始版本的 UCIe 來自英特爾�,英特爾將規(guī)范貢獻給業(yè)界,并將成為 UCIe 聯(lián)盟��。幾十年來����,英特爾一直負責(zé)多項備受矚目的開放式互連技術(shù)的初步開發(fā)——其中最重要的是 USB、PCIe 和 Thunderbolt 3�。但即使如此,在他們看中的下一波計算浪潮技術(shù)的基礎(chǔ)上��,看到他們捐贈零差距互連技術(shù)來幫助行業(yè)發(fā)展依然會讓人有少許震驚�。不過,請不要誤會,這不是英特爾獨有的舉措���,支持新標(biāo)準(zhǔn)的公司以及即將組建的聯(lián)盟就是明證�����。(只要你看到有來自英特爾和 AMD 的高級研究員在同一個簡報電話中����,你就知道發(fā)生了大事)

UCIe 借鑒了英特爾早期的高級接口總線 (AIB) 技術(shù)���。英特爾此前曾在 2020 年將該技術(shù)捐贈給 CHIPS 聯(lián)盟�����,因此這不是英特爾第一次以開放的方式發(fā)布該技術(shù)的一個版本��。但 UCIe 是迄今為止規(guī)模最大(也是最專注于小芯片)的努力����,英特爾的晶圓廠競爭對手以及 CPU 設(shè)計競爭對手的支持就是明證�����。

至于UCIe規(guī)范本身�����,我們來談?wù)勊隽耸裁?��,不包括什么��。該?guī)范涵蓋了物理層��,列出了小芯片相互通信的電氣信號標(biāo)準(zhǔn)���,以及物理通道的數(shù)量和支持的凸塊間距。該規(guī)范涵蓋了協(xié)議層�����,定義了覆蓋在這些信號上的更高級別的協(xié)議�����,以了解所有內(nèi)容并提供必要的功能集����。

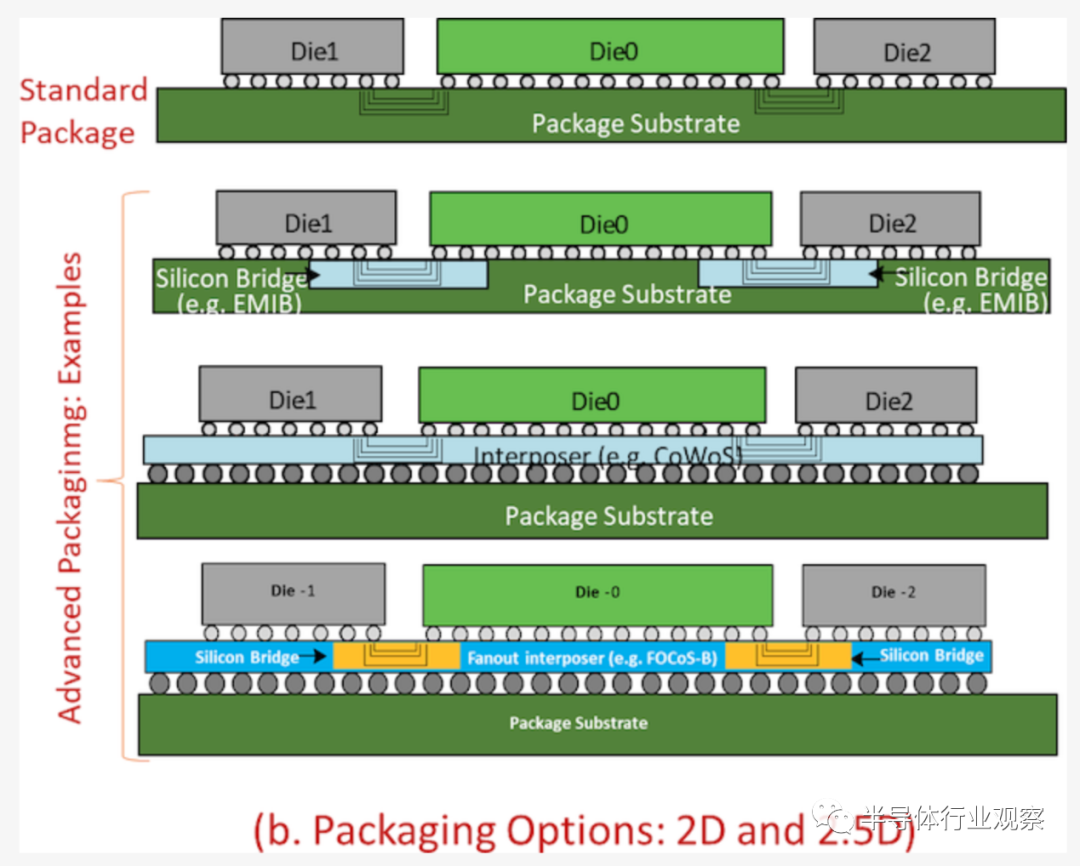

然而�����,規(guī)范沒有涵蓋的是用于在小芯片之間提供物理鏈接的封裝/橋接技術(shù)���。例如,這不是英特爾放棄 EMIB 或 Foveros����。相反,UCIe 與橋接無關(guān)���。小芯片可以通過扇出橋��、硅中介層����、EMIB 連接���,甚至在帶寬較低的設(shè)備的情況下�,甚至只是一個普通的舊有機基板��。UCIe 旨在與所有這些一起工作�����,因為橋本身本質(zhì)上是一個dumb pipe ��,用于在小芯片之間傳輸電信號�。只要一個小芯片符合標(biāo)準(zhǔn)(包括凸塊間距),它就可以與另一個 UCIe 小芯片通信����。

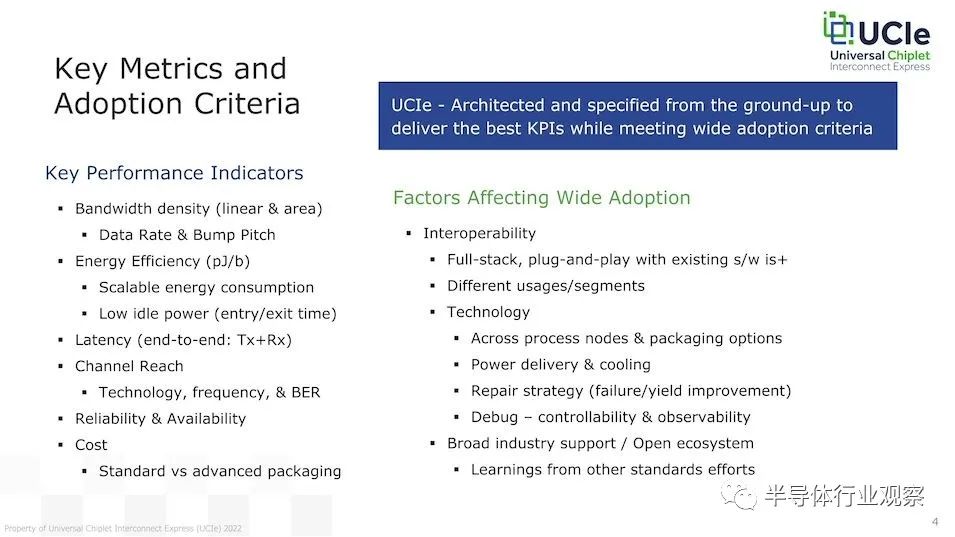

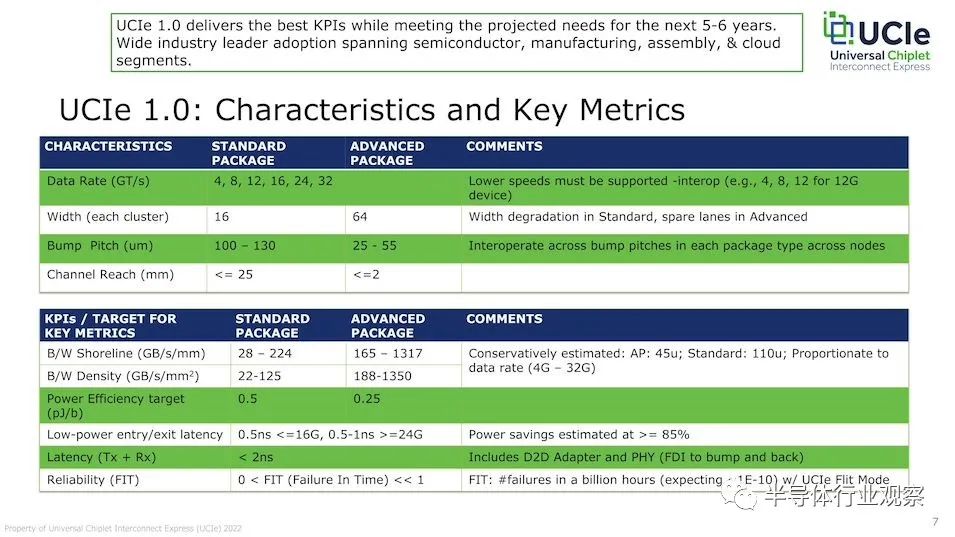

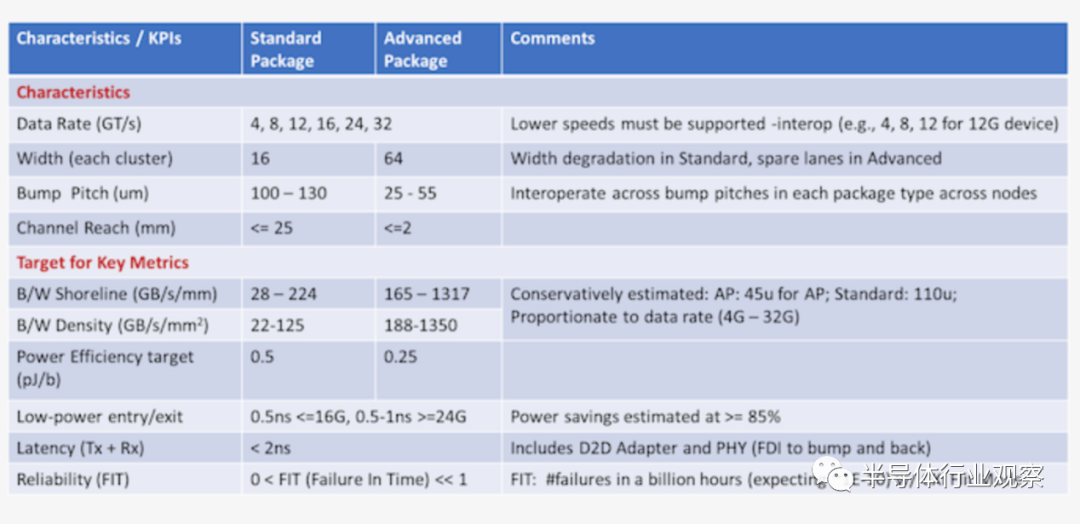

關(guān)于這一點,UCIe 1.0 基本上具有兩個性能/復(fù)雜性標(biāo)準(zhǔn)級別��。恰當(dāng)命名的“標(biāo)準(zhǔn)封裝”級別的規(guī)格是為使用傳統(tǒng)有機基板的低帶寬設(shè)備設(shè)計的���。這些部件將使用多達 16 條數(shù)據(jù)通道��、100μm + 凸塊間距和擴展通道長度�����。在高層次上��,這就像通過現(xiàn)代 PCIe 鏈路連接兩個設(shè)備����,但將它們放置得更近了。

同時�����,第二套規(guī)范涵蓋了 UCIe 小組看似“高級封裝”的內(nèi)容�����,涵蓋了所有基于高密度硅橋的技術(shù)�����,如 EMIB 和 InFO�����。先進的封裝規(guī)格要求更小的凸塊間距(大約 25μm 到 55μm)以及由于更高的密度和小于 2mm 的非常短的通道范圍���,每個集群的通道數(shù)是 4 倍��。UCIe 推廣者采用最全面的配置�,相信采用當(dāng)今 45μm 凸點間距技術(shù)的先進封裝設(shè)置將能夠提供高達 1.3TB/s/mm 的“ shoreline”(線性)帶寬��。也就是說���,每秒1.3TB的數(shù)據(jù)可以從芯片的1mm邊緣通過����。

我不會在這里對每一個數(shù)字都詳細解讀����,但可以肯定的是,所有這些都是為了強調(diào) UCIe 是如何設(shè)置為滿足性能范圍兩端的小芯片需求的�。對于只需要以具有成本效益的方式將兩個小芯片組合在一個封裝上的芯片制造商來說,有標(biāo)準(zhǔn)封裝方法���。對于需要使兩個小芯片的性能盡可能接近單個單片芯片的芯片制造商來說����,先進的封裝規(guī)范允許大量通道�����,從而提供大量帶寬����。

同時,有趣的是要注意發(fā)起人在延遲和能源效率方面的期望��。對于所有封裝類型,延遲預(yù)計將低于 2ns��,這在拆分以前單片芯片設(shè)計的小芯片設(shè)計中尤其重要����。同時,電源效率范圍從標(biāo)準(zhǔn)封裝的低 0.5 pJ/bit 到高級封裝的更低 0.25 pJ/b�。這有助于說明為什么一些芯片制造商渴望加入小芯片,因為對離散 PCIe/CXL 卡的改進可能是顯著的�����。

反過來��,連接小芯片的物理層對于 UCIe 來說是新的�����。英特爾和其他推動者并沒有深入探討其工作原理����,但在較高級別上,物理層標(biāo)準(zhǔn)提供了電信號�、時鐘、鏈路訓(xùn)練和邊帶信號。一個 256 字節(jié)的流控制單元 (FLIT) 依次處理實際的數(shù)據(jù)傳輸�����。

在此之上是一個中間層�,該組織稱之為 Die-to-Die Adapter。D2D 為小芯片之間的鏈路狀態(tài)管理和參數(shù)協(xié)商提供了基礎(chǔ)����。D2D 還負責(zé)通過 CRC 和鏈路級重試為額外的數(shù)據(jù)可靠性保護提供可選支持���。

最后��,在協(xié)議層�����,小芯片制造商有幾個不同的選擇�。UCIe 的官方標(biāo)準(zhǔn)化協(xié)議是 PCI-Express 及其緩存一致的“表親”��,Compute Express Link�����,它本身構(gòu)建在 PCIe 之上�����。在這里討論他們的選擇時,UCIe 的推動者選擇了務(wù)實的方法:PCIe 和 CXL 已經(jīng)得到了全行業(yè)的支持��,因此他們不會自己重新發(fā)明輪子���,而是要利用協(xié)議層的現(xiàn)有生態(tài)系統(tǒng)���。這意味著 UCIe 正在以一個完全充實且經(jīng)過充分驗證的協(xié)議層開始運行,該協(xié)議層可以提供可靠的數(shù)據(jù)傳輸和鏈路管理����,以及緩存一致性等額外的定制功能。也許同樣重要的是����,這意味著客戶和芯片制造商都可以利用他們現(xiàn)有的 PCIe/CXL 軟件投資,

在實踐中��,如果 UCIe沒有以這種方式利用 PCIe/CXL ����,我會感到更加驚訝。PCIe 技術(shù)已成為其他各種技術(shù)的支柱,整個行業(yè)已經(jīng)不再試圖在基本設(shè)備互連需求方面超越 PCIe����。

也就是說,發(fā)起人已經(jīng)明確表示�����,UCIe 并不僅限于 PCIe/CXL�。如果出現(xiàn)某些問題并且所有者愿意將其捐贈給該標(biāo)準(zhǔn),則該標(biāo)準(zhǔn)的未來版本可能會添加其他協(xié)議�。

最后,芯片制造商也可以自由使用他們自己的定制/定制協(xié)議����;它們不僅限于使用PCIe /CXL��。UCIe 支持允許使用任何其他協(xié)議的原始/流式協(xié)議選項����。當(dāng)然,兩個小芯片都需要支持這種自定義協(xié)議才能建立連接�,但即使在這種情況下,這也將允許芯片制造商利用 UCIe 標(biāo)準(zhǔn)的物理方面來簡化他們自己的設(shè)計/生產(chǎn)�����。

這也意味著現(xiàn)有的互連協(xié)議,例如 AMD 的 Infinity Fabric�����,即使引入了 UCIe�,也不太可能出現(xiàn)在任何地方。像 IF 這樣的協(xié)議仍然比 PCIe/CXL 的能力要復(fù)雜和專業(yè)得多�,考慮到連接 CPU 內(nèi)核和 I/O 芯片的非常具體的一致性要求,這是有道理的����。換句話說,chiplet 設(shè)計的最前沿仍然領(lǐng)先于 UCIe 1.0 的起點����。

長期發(fā)展:UCIe 也適用于外部互連?��!

盡管 UCIe 的首要重點是為小芯片提供片上互連��,但該標(biāo)準(zhǔn)實際上包含了片外的規(guī)定���。芯片外的方式��。

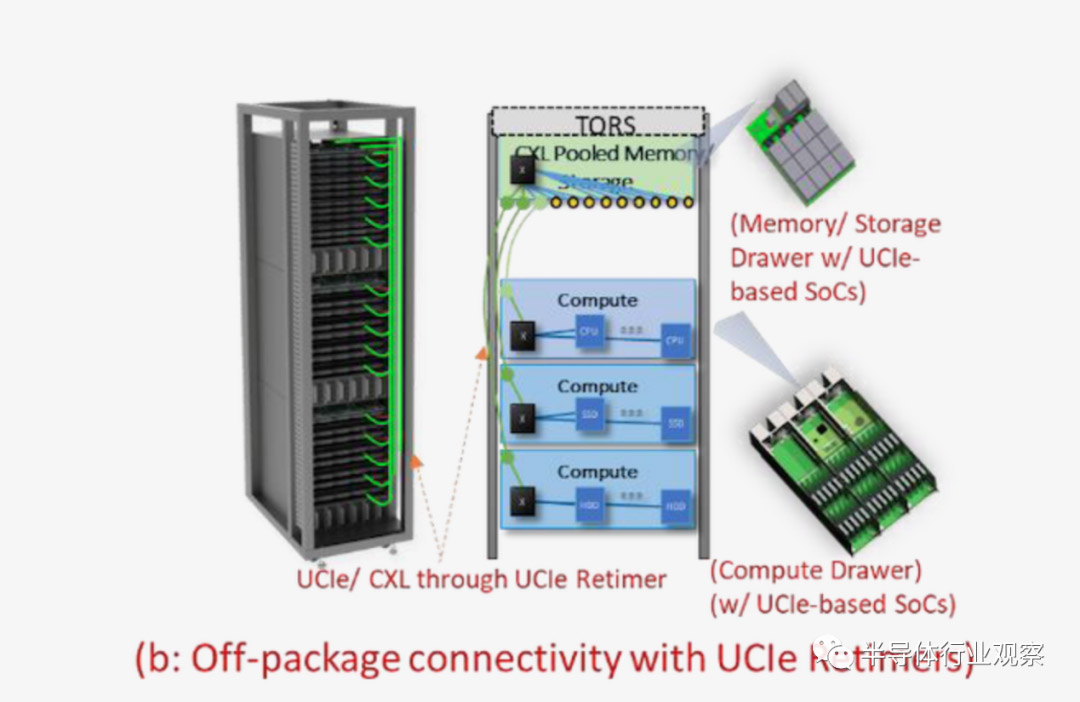

如果芯片/系統(tǒng)制造商愿意��,該規(guī)范允許使用重定時器在協(xié)議級別傳輸更遠距離的 UCIe�����。誠然���,這確實通過增加(很多)距離而犧牲了延遲和功率優(yōu)勢�。但是 UCIe 推廣者設(shè)想服務(wù)器客戶使用它在機架或 pod 級別提供 UCIe 連接���,即使在長距離上也能提供直接的小芯片到小芯片的連接��。

這種設(shè)置最有趣和最明顯的用例是硅光子學(xué)����。在那里擴展小芯片概念��,芯片制造商可以在封裝邊緣構(gòu)建一個共同封裝的光收發(fā)器�,然后使用 UCIe 將其連接到另一個小芯片�。這將允許直接從芯片進行光學(xué)互連,繞過使用片外收發(fā)器的需求(和電力成本)��。

發(fā)起人還展示了基于外部存儲器/存儲設(shè)備的概念。以及帶有更多 SoC 的外部機架/繪圖���。

UCIe 1.0 只是一個開始

雖然今天發(fā)布了 UCIe 1.0 規(guī)范���,但該標(biāo)準(zhǔn)的推動者已經(jīng)將目光投向了該技術(shù)以及聯(lián)盟本身的未來。

UCIe 1.0 在很大程度上是一個“起點”標(biāo)準(zhǔn)�����,它最初是在英特爾內(nèi)部以單獨的方式開發(fā)的��。如前所述����,該聯(lián)盟將研究其他可能的協(xié)議添加到標(biāo)準(zhǔn)中。到目前為止��,該標(biāo)準(zhǔn)只定義了他們認(rèn)為是小芯片設(shè)計的四個方面中的兩個:物理層和通信協(xié)議�����。該小組希望通過定義標(biāo)準(zhǔn)化的小芯片形狀因素���,甚至管理其他小芯片�����,進一步使混合搭配的小芯片生態(tài)系統(tǒng)成為現(xiàn)實���。

這是在芯片封裝技術(shù)不斷變化的基礎(chǔ)上����,這些技術(shù)仍在進步����。UCIe 1.0 標(biāo)準(zhǔn)基本上只針對 2D 和 2.5D 芯片封裝定義,而不是像即將推出的 Foveros Direct 這樣的 3D 直接芯片對芯片技術(shù)����。隨著 3D 芯片封裝的推出,標(biāo)準(zhǔn)將需要更新以考慮提供的新功能以及更高的密度�。

但為此,UCIe 將需要一個合適的聯(lián)盟來支持它����,這就是為什么今天的公告既是對新標(biāo)準(zhǔn)的啟示���,也是對其他公司加入并幫助開發(fā)標(biāo)準(zhǔn)的未來迭代的宣傳���。UCIe 發(fā)起人團體已經(jīng)是一個非常龐大的名單�����,其中包括芯片/IP 設(shè)計師 AMD����、Arm�、英特爾和高通、芯片工廠臺積電和三星(和英特爾)���、芯片封裝公司 Advanced Semiconductor Engineering 和云計算提供商谷歌��、微軟和 Meta的支持�。